Оперативна пам'ять

- Еволюція динамічної пам'яті

- Таблиця 1. Прогноз зміни типів пам'яті

- Extended Data Out DRAM

- Burst EDO DRAM

- Synchronous DRAM

- Double Data Rate SDRAM

- Direct Rambus

- Мікросхеми і модулі

- Характеристики швидкодії SDRAM

- Таблиця 2. Характеристики динамічної пам'яті різних технологій

- виробництво пам'яті

Головна → технології → Оперативна пам'ять

Андрій Борзенко

Пам'ять - один з основних компонентів будь-якого комп'ютера, будь то кишеньковий ПК або потужний сервер. У міру подальшого збільшення швидкодії мікропроцесорів ефективну швидкодію елементів пам'яті часто стає вузьким місцем комп'ютерних систем.

Зазвичай розглядають модель чотирирівневої ієрархії пам'яті: кеш-пам'ять першого рівня (сверхоперативная L1), кеш-пам'ять другого рівня (сверхоперативная L2), основна (оперативна) і зовнішня пам'ять (жорсткі диски). В якості основних критеріїв при такому розподілі виступають швидкодія і ціна; остання, в свою чергу, впливає на типові розміри конкретного виду пам'яті. [ 1 ].

Сучасна індустрія постійно вводить у вжиток нові технології, і засновані на них пристрої, що запам'ятовують розрізняються за багатьма параметрами, починаючи з архітектурних особливостей і закінчуючи форм-фактором монтажного модуля пам'яті. [ 2 ]

Еволюція динамічної пам'яті

Для динамічної пам'яті пряме скорочення часу доступу технологічно досить складно і призводить до різкого зростання вартості. Саме тому основний упор робиться на різні схемотехнічні прийоми - конвеєрний режим, чергування адрес, організацію банків і т. П. Розглянемо основні типи динамічної пам'яті, які використовувалися раніше і до цих пір застосовуються в комп'ютерних системах (передбачувані терміни заміни їх на найсучасніші наведені в табл. 1).

Таблиця 1. Прогноз зміни типів пам'яті

Платформа 2001 2002 2003 Настільні ПК SDRAM DDR DDR Сервери SDRAM SDRAM / DDR DDR Робітники станції RDRAM / PC133 RDRAM / DDR RDRAM / DDR Портативні ПК SDRAM DDR DDR Інші комп'ютери SDRAM SDRAM / DDR DDRFast Page Mode DRAM

Технологія FPM DRAM свого часу дозволила значно - в порівнянні з більш ранньої реалізацією DRAM - прискорити доступ до послідовно розташованим (в межах сторінки) комірок пам'яті. Нагадаємо, що в матриці динамічної пам'яті зчитування в статичний буфер відбувається для всієї рядки цілком, конкретний ж біт вибирається вже адресою стовпця. Зрозуміло, що якщо наступний підлягає зчитуванню біт знаходиться в тому ж рядку, то немає сенсу читати її в буфер ще раз. FPM DRAM використовувалася в комп'ютерах класу до Pentium-100. Типове значення часу доступу - 60-70 нс. FPM DRAM змінила звичайну DRAM, яку використовували в комп'ютерах на базі мікропроцесорів 8086/88 і 80286, і використовувалася в персональних комп'ютерах приблизно до 1994 г.

Extended Data Out DRAM

На відміну від звичайної пам'яті з сторінкової організацією EDO DRAM оснащується додатковим набором регістров- «засувок», завдяки яким дані на виході можуть утримуватися навіть протягом наступного запиту. Такого ефекту можна домогтися на FPM DRAM тільки в режимі чергування адрес. Нагадаємо, що в будь-якому зверненні до пам'яті можна виділити три фази - 1) початок доступу, 2) період, коли дані стають дійсними, і 3) безпосередньо передачу. Ці фази повторюються послідовно для кожного осередку в зчитується рядку. У випадку з EDO-пам'яттю тимчасові параметри (а отже, і швидкодія) поліпшуються за рахунок виключення циклів очікування в фазі готовності даних. Типові часи доступу - 45, 50, 60 і 70 нс.

Burst EDO DRAM

У пам'яті типу BEDO, на відміну від EDO DRAM, вибірка чотирьох операндів команди передачі даних відбувається автоматично. BEDO DRAM була розроблена як альтернатива синхронної пам'яті, проте не отримала підтримки розробників наборів мікросхем, і до того ж у неї була невисока максимальна тактова частота (66 МГц), так що вона не знайшла широкого поширення.

Невисока швидкодія підсистеми пам'яті з модулями DRAM було обумовлено неможливістю точної синхронізації частоти процесора і швидкості обробки даних в осередках пам'яті. При зчитуванні не можна було сказати, звідки в наступний раз буде братися інформація - з іншого банку або з сусідньої комірки, - і скільки часу на це буде потрібно. До того ж під час звернення до пам'яті процесор не міг працювати з іншими компонентами системи, що, природно, знижувало продуктивність.

Synchronous DRAM

Цей тип пам'яті дозволив ще більше підняти швидкодію. SDRAM використовує ступінчасту конвеєрну архітектуру і, крім того, внутрішній доступ типу «пінг-понг» до блокам пам'яті з чергуванням адрес. Синхронізація роботи пам'яті SDRAM здійснюється зазвичай частотою системної (зовнішньої) шини. SDRAM працює приблизно так само, як і стандартна DRAM, - здійснюючи доступ до рядків і колонок осередків даних. Але в SDRAM застосований специфічний механізм синхронного функціонування банків осередків, який в поєднанні з пакетним режимом ефективно усуває стану затримок і очікування. Коли процесору необхідно отримати дані з оперативної пам'яті, він може отримати їх в необхідний момент. Таким чином, хоча фактичний час обробки даних не змінилося, ефективність вибірки і передачі даних підвищилася. Завдяки жорсткій синхронізації контролер пам'яті точно «знає», коли така інформація буде оброблена. Це звільняє процесор від станів очікування. Затримки в SDRAM ефективно усуваються завдяки синхронного функціонуванню блоків осередків. Оскільки робота пам'яті і процесора узгоджується системним таймером, то в кінці кожного такту на висновках модуля пам'яті з'являється сигнал готовності даних, отже, процесорний час витрачається лише на цикли читання-запису. Крім того, конвеєрна адресація забезпечує доступ до наступного блоку запитаної інформації до завершення обробки попереднього.

Double Data Rate SDRAM

Взагалі кажучи, звичайну синхронну пам'ять правильніше називати SDR (Single Data Rate) SDRAM. Синхронна пам'ять з подвоєною швидкістю (DDR) зберегла архітектуру, кількість банків і сам технологічний процес виробництва SDRAM, однак наявні в ній схемотехнические удосконалення дозволяють істотно збільшити її швидкодію. Зокрема, тут використовується ще більш жорстка синхронізація роботи пристрою. У функціональну структуру введені схеми фазового автопідстроювання частоти DLL (Delay Locked Loop), що забезпечують для сигналів стробування даних цикл з фіксованою затримкою. Ці сигнали допомагають контролеру пам'яті більш точно синхронізувати дані, що надходять від різних модулів пам'яті, що знаходяться в одному банку. Мікросхеми DDR SDRAM фактично збільшують швидкість доступу до даних вдвічі в порівнянні з SDRAM, використовуючи при цьому одну і ту ж частоту. Справа в тому, що застосування DDR SDRAM дає можливість читати інформацію як по передньому, так і по задньому фронту сигналу таймера. Крім того, частота операцій підвищується за рахунок використання інтерфейсних логічних схем з низьким годує напругою. Якщо для SDRAM зазвичай використовуються схемотехнічні рішення на базі низкоуровневой транзисторних-транзисторної логіки LVTTL (Low Volt Transistor-to-Transistor Logic) з напругою живлення 3,3 В, то в DDR SDRAM застосовується спеціальна логіка SSTL (Stub Series Terminated Logic) з напругою 2 , 5 В.

Direct Rambus

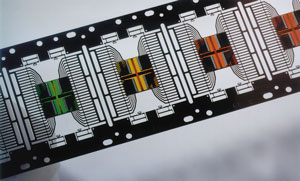

Відомо, що існує тільки два способи підвищення пропускної спроможності будь-якої комп'ютерної підсистеми - це або підвищення частоти роботи шини, або збільшення її розрядності. Одночасне збільшення обох параметрів досить проблематично. Саме ця обставина змушує розробників йти на компроміс. На противагу технології SDRAM, що використовує 64-розрядну магістраль і частоти до 133 МГц, технологія Rambus надає 16-розрядну шину даних і ефективні частоти до 800 МГц відповідно. Вузька шина і висока частота значно збільшують ефективність використання пам'яті та оптимізують її завантаження, максимально звільняючи протокол від тимчасових затримок. Direct Rambus дозволяє досягти дуже великих швидкостей передачі даних: до 1,6 Гбайт / с на один канал і до 6,4 Гбайт / с при чотирьох каналах. Вся підсистема DR складається з наступних компонентів: основний контролер (Rambus Memory Controller, RMC), канал (Rambus Channel, RC), роз'єм для модулів (Rambus RIMM Connector, RRC), модуль пам'яті (Rambus In-line Memory Module, RIMM, рис . 1), генератор диференціальних імпульсів (Direct Rambus Clock Generator, DRCG) і мікросхеми пам'яті (Direct Rambus DRAM, DRDRAM). Фізичні, електричні і логічні інтерфейси, застосовувані в системі, визначені компанією Rambus ( http://www.rambus.com ) І повинні строго виконуватися всіма виробниками для дотримання абсолютної сумісності її частин. Система функціонує на частоті 800 МГц (PC800), синхронізуючись сигналом 400 МГц. Модулі RIMM нового покоління тактуються частотою 533 МГц, за рахунок чого забезпечується більш висока пропускна здатність (специфікація PC1066). У цих модулях задіяна 4-банкова архітектура 4i (4 independent bank), що дозволяє знизити собівартість RIMM.

Мал. 1. RIMM-модуль.

Сигнальний протокол Direct Rambus заснований на електричному інтерфейсі RSL (Rambus Signaling Levels), що дає можливість за допомогою технології подвоєною передачі даних (DDR) отримати результуючу частоту 800 МГц і використовувати стандартний КМОП-інтерфейс сигналів введення-виведення ядра ASIC (Application Specific Integrated Circuit). Високошвидкісний протокол сигналів RSL використовує низьковольтні напруги логічних рівнів.

Оперативна пам'ять ядро мікросхем має многобанковую організацію. При цьому кожен банк може мати як виділені, так і спільно використовуються підсилювачі зчитування, завдяки чому в мікросхемі може бути активована кілька банків одночасно.

Канал DRDRAM є синхронну послідовно-паралельну шину. Він містить 35 активних ліній. З них можна виділити дві роздільні шини - для управління (адреси) і для даних. Перша має ширину 8 біт, з яких 5 відповідають адресою стовпця, а 3 - адресою рядка комірки пам'яті. Друга шина має 16 розрядів. Передача всіх сигналів в каналі відбувається в напрямку поширення тактовихімпульсів, які від генератора спочатку надходять на дальній від контролера модуль пам'яті. Після досягнення контролера напрямок їх руху змінюється на протилежне. Всі сигнальні шини проходять через модулі і закінчуються на термінаторі. Система пам'яті не може функціонувати за наявності порожніх роз'ємів, тому такі роз'єми заповнюються спеціальними заглушками. Дані та адреси передаються по каналу пакетами. Функції по їх обробці покладені на контролер, до складу якого входить мультиплексор-демультиплексор. Він здійснює операції упаковки і розпаковування на кордоні між вузьким послідовним потоком даних в каналі і більш широким синхронним паралельним в самому контролері.

Нововведенням для технології пам'яті стало використання в DRDRAM чотирьох режимів енергоспоживання - активного (Active), очікування (Standby), економного (Nap) і сну (PowerDown). У першому режимі DRDRAM може миттєво обробити запит на передачу даних. Природно, цей режим характеризується найвищим енергоспоживанням. Режим Standby - це звичайний стан очікування запиту. У ньому знаходяться всі пристрої, які не беруть участі в передачі. На відміну від звичайних систем пам'яті на основі DRAM, де всі пристрої, що входять до банку, споживають енергію під час операцій запису-читання, в пам'яті типу Rambus це відбувається тільки з одним пристроєм - інші переходять в режим очікування, що є основним. Режими Nap і PowerDown ще більш економні. Між собою вони різняться рівнем споживання і швидкістю переходу в активний стан.

Мікросхеми і модулі

Ємність мікросхем пам'яті традиційно вимірюється в бітах, а ось стосовно до модулів використовують байти (1 Мбайт = 8в1 Мбіт). Позначення 1 МХ4 означає, що дана мікросхема може адресувати один мегабіт осередків, в кожній з яких може зберігатися 4 біти інформації. Кажуть також, що ємність такої мікросхеми 4 Мбіт. Як правило, ємність мікросхем пам'яті зростає з инкрементом 4. Справа в тому, що додавання однієї адресної лінії дозволяє збільшити кількість рядків (і стовпців) в матриці пам'яті вдвічі, всього ж її розмір зростає вчетверо.

Кожен кристал пам'яті (рис. 2) складається з ячейок, в яких може зберігатися кілька розрядів даних. Наприклад, 16-Мбіт кристал може бути налаштований як 4 Мбіт x 4, 2 Мбіт x 8 або 1 Мбіт x 16, але у всіх випадках його загальна ємність дорівнює 16 Мбіт. Число розрядів на осередок показує, скільки біт передається одночасно при зверненні до неї. Мікросхеми пам'яті поміщають в корпусу для поверхневого монтажу на друкованих платах типу SOJ (Small Outline J-lead), TSOP (Thin Small Outline Package) або CSP (Chip Scale Package). Маркування, нанесена на корпус будь-якої мікросхеми, як правило, містить спеціальні позначення, що включають, наприклад, країну, найменування (або логотип) фірми-виробника, дату випуску і т. П. Але найголовніше - вона несе в собі інформацію про тип пам'яті, ємності, часу доступу і інших архітектурних і технологічних подробицях.

Мал. 2. Кристали пам'яті на підкладці.

Елементи динамічної пам'яті для перших персональних комп'ютерів конструктивно були виконані у вигляді окремих мікросхем в корпусах типу DIP (Dual In line Package), які встановлювалися на системну плату в спеціальні посадочні місця або розпаювали. Потім на зміну окремим мікросхемах прийшли модулі пам'яті типу SIPP (Single In line Pin Package), SIMM (Single In line Memory Module) і DIMM (Dual In line Memory Module). Ці модулі є невеликі текстолітові плати з друкованим монтажем і встановленими на них мікросхемами пам'яті. Для підключення до системної плати на SIMM- і DIMM-модулях використовується друкований ( «ножовий») роз'єм, а на SIPP-модулях - штирьовий. SO DIMM (Small Outline DIMM) - це різновид DIMM-модулів малого розміру, призначена в першу чергу для портативних пристроїв. Найбільш часто зустрічаються 72- і 144-контактні модулі (розрядність відповідно 32 і 64 біт).

Для сучасних модулів пам'яті використовуються багатошарові друковані плати. Стандарти пред'являють спеціальні вимоги до верствам, відстані між доріжками і якості розводки. Більшість друкованих плат мають чотири шари (два сигнальних, харчування і «маса»). Сигнали і харчування і маса повинні бути розведені по різних верств. Окремі фірми-виробники плат використовують шестишарові друковані плати, де кожен сигнальний шар розташовується між шарами маси і харчування, що зменшує можливість виникнення шумів і електромагнітних наведень між лініями.

У DIMM-модулів, на відміну від SIMM, контакти на протилежних сторонах плати електрично не пов'язані між собою. Це дає можливість практично вдвічі збільшити кількість висновків модуля. Самі мікросхеми пам'яті також встановлюються на платі з двох сторін. Варто відзначити, що по форм-фактору DIMM-модулі DDR SDRAM відрізняються від SDRAM: число контактів в них збільшилася з 168 до 184, а змінилося становище ключа не дозволяє вставити модулі DIMM DDR в роз'єми для SDRAM.

Модулі DIMM підрозділяються по напрузі харчування і здатності навантаження (Буферізірованний і небуферізірованние). Модулі з високою здатністю навантаження зазвичай застосовуються в системах з великим об'ємом пам'яті, так як через високу електричної ємності модулів пам'яті час їх підзарядки (а пам'ять потрібно завжди заряджати, щоб вона не очистилася) стає дуже великим, що призводить до втрати тактів і взагалі значною кількістю помилок. Буферні мікросхеми зберігають дані, що надійшли досить швидко, звільняючи контролер від зайвого навантаження. Зрозуміло, що через додаткових затримок продуктивність такого роду пам'яті трохи нижче. Перше покоління таких модулів носило назву Buffered DIMM і використовувалося з пам'яттю типу FPM і EDO. Друге покоління DIMM дозволило, поряд з пам'яттю EDO і FPM, використовувати SDRAM, а аналогом пам'яті Buffered для другого покоління стала так звана пам'ять типу Registered. Як буферів зазвичай використовуються мікросхеми приймально-передавальних пристроїв (шинних підсилювачів).

Для найбільш відповідальних додатків, де ціна помилки дуже висока, використовуються не звичайні модулі з перевіркою на парність, а модулі з корекцією помилок ECC (Error Correction Code). Нагадаємо, що ідея, що лежить в основі методу ECC, досить проста - кожен розряд пам'яті відповідає більш ніж в одну контрольну суму. Це вимагає збільшення числа контрольних розрядів, але дає можливість відновлювати значення збійного біта по незбіжним контрольних сумах. Отже, ECC використовує один розряд парності на байт інформації для знаходження одиночних помилок, а для виправлення потрібно 7 біт для 32- і 8 біт для 64-розрядної пам'яті. При цьому легко виявляються подвійні помилки.

Перспективною технологією запобігання помилок в пам'яті вважається IBM Chipkill. При її використанні відмова окремої мікросхеми, незалежно від її розрядності, не зачепить більше одного розряду в будь-якому з слів ECC. Наприклад, в 4-розрядної мікросхемі DRAM окремі біти з усієї четвірки потрапляють в різні слова ECC, т. Е. В різні адресні простори пам'яті. Тому навіть у разі повної відмови мікросхеми кількість помилкових розрядів в словах ECC не перевищить одиницю, а таку помилку механізм ECC усуває автоматично.

Жоден сучасний модуль пам'яті НЕ может обійтіся без такого компонента, як мікросхема SPD (Serial Presence Detect - послідовне визначення наявності). Інтерфейс послідовного детектування, регламентованості на Сейчас для всіх модулів пам'яті форм-фактора SIMM / DIMM / RIMM, вікорістовує двухпроводной протокол управління системою (SMBus, System Management Bus). Протокол Сумісний зі спеціфікацією Inter-IC (I2C або IIC), з его помощью Прості мікросхеми могут спілкуватися з іншою частина системи. Принцип використання шини SMBus у разі SPD зводиться до передачі даних від мікросхеми ППЗУ (EEPROM), встановленої на модулі, відповідним регістрів контролера пам'яті, що входить до складу «північного» мосту або концентратора контролерів основних інтерфейсів. Дані передаються через SMBus-інтерфейс об'єднаного контролера периферійних компонентів ( «південний» міст або концентратор контролерів вводу-виводу) за допомогою системного BIOS. Таким чином, система отримує всі необхідні дані про модулі і налаштовується на оптимальний режим роботи відповідно до записаним в мікросхему SPD значенням. Всі модулі, що підтримують схему послідовного детектування, повинні в обов'язковому порядку підтримувати операції записи сторінки як мінімум чотирьох послідовних адрес. Сама схема SPD характеризується інтерфейсним протоколом, розміром карти програмування, типом використовуваних даних і змістом. Інтерфейсний протокол (SPD Interface Protocol) характеризує електричні, геометричні та фізичні параметри використовуваної мікросхеми ППЗУ.

Характеристики швидкодії SDRAM

Кожен модуль синхронної пам'яті має ряд характеристик, основні з яких - його тимчасові параметри і частота (табл. 2). Частота вимірюється в мегагерцах і визначає продуктивність даного типу пам'яті. Так, DDR SDRAM з тактовою частотою 133 МГц (ефективна 266 МГц) забезпечує пропускну здатність шини пам'яті до 2,1 Гбайт / с. Якщо в специфікації Rambus DRAM за основу береться результуюча частота (тактова частота, помножена на два пакети даних за такт, наприклад, PC800), то для позначення DDR SDRAM часто використовують пікову пропускну здатність. Наприклад, модуль пам'яті DDR SDRAM з тактовою частотою 100 МГц (8 байт x 200 МГц = 1600. Мбайт / с) буде позначатися PC1600.

Таблиця 2. Характеристики динамічної пам'яті різних технологій

Тип пам'яті Ширина шини, біт Обмеження по швидкості Пікова пропускна здатність, Мбайт / с FPM DRAM 64 60-70 нс 200 EDO DRAM 64 45-50 нс 320 PC66 SDRAM 64 66 МГц 528 PC100 SDRAM 64 100 МГц 800 PC133 SDRAM 64 133 МГц 1 060 DDR200 SDRAM (PC1600) 64. 100 МГц (х2) 1600 DDR266 SDRAM (PC2100) 64. 133 МГц (х2) 2100 DDR333 SDRAM (PC2700) 64. 166 МГц (х2) 2700 DDR400 SDRAM (PC3200) 64. 200 МГц (х2) 3200 Rambus DRAM (PC800) 16 400 Мгц (х2) 1600Зауважимо, що набір мікросхем Intel 850 має два незалежні канали для роботи з пам'яттю Rambus, так що загальна пропускна здатність становить 3200 Мбайт / с (1600 Мбайт / с х2).

Серед часових параметрів мікросхем (і модулів) пам'яті зазвичай виділяють CAS Latency (CL), RAS-CAS Delay (tRCD) і RAS Precharge (tRP). [ 3 ] Параметр CL визначає затримку, необхідну для видачі сигналу CAS, т. Е. Кількість тактів від моменту запиту даних до їх зчитування з модуля пам'яті. Час tRCD - це затримка між сигналами RAS і CAS, що визначає кількість тактів, необхідних для завдання сигналів RAS і CAS контролером пам'яті. Параметр tRP визначає мінімальний час (в тактах) паузи між командами. Затримка CL для SDRAM становить 2-3 такту, а для DDR SDRAM - 2-2,5. [ 4 ]

виробництво пам'яті

Кристали пам'яті - це вироби високого технологічного рівня, які випускаються невеликою кількістю всесвітньо відомих японських, корейських, американських і європейських фірм - Fujitsu, Hynix (Hyundai), LG, Micron Technology, Mitsubishi, Elpida Memory (NEC, Hitachi), Oki, Panasonic, Samsung Electronics, Infineon, Texas Instruments, Toshiba. Їх зазвичай називають major brand, або просто major. Всі ці компанії мають власне напівпровідниковий виробництво. Вони проводять ретельне вихідне тестування мікросхем, але продукція, що випускається успішно проходить далеко не всі випробування.

Теоретично кожен кристал по виходу з виробничої лінії повинен бути перевірений на надійність і швидкодію відповідно до специфікації. Однак всю виходить продукцію зазвичай умовно поділяють на три частини. В першу потрапляють кристали, які пройшли всі етапи тестування, в другу - мікросхеми з невеликими відхиленнями від заданих параметрів, а в третю - все решта. Мікросхеми першого класу найбільш надійні і вважаються виробами вищої якості. Вони також найбільш дороги, тому що забезпечують стійку роботу в будь-яких умовах. Такі кристали використовуються самими фірмами-виробниками пам'яті і поставляються за контрактами, практично не потрапляючи на вільний ринок. Кристали другого класу, природно, дешевше - вони скуповуються компаніями, які випускають недорогу пам'ять. Найменшу ціну мають мікросхеми, які на швидкість і надійність не тестувалися.

Часто говорять про модулях пам'яті Original (Major on Major), т. Е. Модулях з мікросхемами Major Brand, виготовленими самою фірмою - виробником мікросхем пам'яті. Це найякісніша, але і найдорожча пам'ять. Модулі типу Major (Major on Third Party) з мікросхемами від фірми-виробника випускаються сторонніми фірмами. З урахуванням того, що в цій пам'яті використовуються висококласні мікросхеми відомих компаній, вона відрізняється від Original лише виготовленням друкованої плати модуля і складанням. Велика частина мікросхем, що виготовляються великими фірмами-виробниками, продається іншим компаніям саме для виробництва модулів за контрактами. Серед відомих фірм-виробників якісних модулів пам'яті слід зазначити такі, як Century Microelectronics, Kingston Technology, Transcend, Smart Modular Technologies і Simple Technology. Зауважимо, що крім так званих стандартних модулів випускаються модулі пам'яті, призначені для конкретних моделей комп'ютерів brandname.

Компанія Kingston Technology ( http://www.kingston.com ), Добре відома своїми високоякісними модулями оперативної пам'яті, була заснована в 1978 г. Вона має регіональні представництва в різних країнах світу і фабрики в США, Ірландії, Тайвані, Малайзії, Китаї. Kingston Technology здійснює поставки в десятки країн світу. На сучасному обладнанні компанія виробляє понад 2 тис. Різних найменувань продукції, сумісних з найрізноманітнішими системами. Всі вироби проходять 100% -ве тестування, виробництво відповідає стандарту ISO 9001, а рівень шлюбу не перевищує 0,1%. Kingston забезпечує довічної гарантією все модулі свого виробництва. Так, модулі пам'яті ValueRAM (рис. 3), виготовлені при дотриманні всіх технологічних норм і гарантованому контролі якості, призначені для застосування в найвідповідальніших системах. Вироби піддаються безлічі перевірочних тестів, зокрема, проходять цикли впливу високих і низьких температур, а також температури та вологості випробування. Додаткова перевірка передбачає вплив різних режимів напруги і температури. Kingston входить до комітету з стандартизації JEDEC, тісно співпрацює з лідерами індустрії.

Мал. 3. Модулі пам'яті ValueRAM.

Тайванська компанія Transcend Information ( http://www.transend.com.tw ), Один з провідних виробників модулів пам'яті, була заснована у 1988 р. Всі модулі виробництва Transcend мають довічну гарантію, а висока надійність продукції забезпечується повним контролем якості на всіх етапах виробництва. Ця компанія першою серед тайванських виробників модулів пам'яті отримала сертифікат відповідності ISO 9001 на своє виробництво. Компанія з головним офісом в Тайбеї має регіональні представництва в США, Німеччині, Нідерландах, Японії, Гонконгу і більш ніж 5 тис. Дистриб'юторів по всьому світу. На сьогодні компанія продає понад 2 тис. Найменувань високоякісної і недорогий пам'яті. Наприклад, для виробництва оперативної пам'яті сімейства JetRam (рис. 4) Transcend закуповує високоякісні компоненти у провідних світових виробників, тестує їх, а потім випускає готові модулі. Ціна на такі модулі значно нижче, ніж на оригінальні, і вони орієнтовані на ринок комп'ютерів і серверів середньої і низької вартості. З метою виявлення неякісних продуктів кожен модуль під час виробництва і безпосередньо перед початком поставок проходить безліч тестів, що включають ретельне динамічне тестування і імітацію роботи в реальних умовах.

Примітки

1. Принцип роботи динамічної пам'яті

Кожен біт динамічної пам'яті представляється як наявність (або відсутність) заряду на конденсаторі, що входить в структуру напівпровідникового кристала. Єдиний спосіб з'ясувати, заряджений або розряджений конденсатор, - спробувати розрядити його. Якщо конденсатор до перевірки був заряджений (т. Е. Зберігав одиничний біт), то після розряду його, зрозуміло, треба знову зарядити.

Осередки пам'яті динамічного типу конфигурируются зазвичай в матрицю рядків і стовпців, причому процес зчитування організовується таким чином, що вміст цілого рядка переноситься в якийсь буфер. Після зчитування відповідного біта вміст буфера перезаписується в ту ж рядок осередків динамічної пам'яті, т. Е. Відбувається перезарядка конденсаторів, які до зчитування були в зарядженому стані. Час зберігання заряду конденсатором обмежена (через паразитних витоків). Щоб не втратити наявні дані, необхідно періодично відновлювати записану інформацію, що і виконується в циклах регенерації.

2. базові поняття

Цикл звернення (access cycle) - час між двома послідовними операціями запису-читання. Розрізняють повні та скорочені цикли. При повному циклі звернення до пам'яті йдуть по випадковим адресами, при скороченому - по послідовним.

Час доступу (access time) - час, необхідний на повний цикл звернення до інформації, що зберігається за випадковим адресою.

Сторінка (page) - набір доступних адрес (стовпців) при фіксованому адресу рядка. Розмір сторінки дорівнює числу стовпців матриці пам'яті.

Асинхронний режим (asynchronous mode) - режим роботи, при якому виконання кожної наступної операції починається після прийому сигналу, яке зазначає на закінчення попередньої.

Синхронний режим (synchronous) - режим, при якому виконання кожної операції починається в фіксовані моменти часу, які визначаються спеціальним тактовим сигналом.

Ширина шини (bus width) - кількість розрядів, які можна передати по шині одночасно.

Банк пам'яті (bank) - 1) блок, область пам'яті; 2) група модулів пам'яті, які повинні бути встановлені на системній платі комп'ютера. Число таких модулів визначається відношенням ширини шини даних мікропроцесора до ширини шини даних модуля.

Чергування (interleave) - спосіб прискорення роботи пам'яті, заснований на припущенні, що читання інформації відбувається по послідовним адресами. Вся пам'ять ділиться на парну кількість банків (2N), а адресний простір розподіляється таким чином, що послідовні адреси знаходяться в різних банках. При послідовному зверненні до даних в режимі чергування можливо отримати до 2N звернень за звичайний цикл. Звернення до банків йдуть, зрозуміло, з невеликим тимчасовим зрушенням.

Пакетний режим (burst mode) - режим, при якому на запит за конкретною адресою повертаються не тільки дані, що зберігаються за цією адресою, але і пакет даних за кількома наступним адресам.

Конвеєрний режим (pipeline) - метод доступу до даних, при якому можна продовжувати операцію читання за попередньою адресою в процесі запиту за наступним.

3. Як працює синхронна пам'ять

Адреса конкретного елементу пам'яті, вміст якої потрібно процесору, встановлюється на шині адреси. Контролер пам'яті декодує цю адресу і визначає, які мікросхеми повинні бути задіяні. Молодша частина адреси, яка визначає рядок пам'ятною матриці, надсилається на мікросхеми. Через деякий час, необхідний для того, щоб сигнали адреси рядка стабілізувалися, контролер пам'яті виставляє стробірующій сигнал RAS (Row Address Strobe - строб адреси рядка). При подачі сигналу на матрицю він активізує цілком весь рядок, при цьому автоматично виконується регенерація всіх осередків на ній. Після цього на мікросхеми надсилається старша частина адреси - «стовпець». А потім, після деякої тимчасової затримки, виставляється стробірующій сигнал CAS (Column Address Strobe - строб адреси стовпця). Стан осередків вибраного стовпця переноситься на вихідні буфера мікросхем, які безпосередньо пов'язані з шиною даних.

4. Що таке QBM

Компанія Kentron Technologies ( http://www.kentrontech.com ) Запропонувала архітектуру пам'яті Quad Band Memory (QBM). Збільшення пропускної здатності DDR SDRAM досягається за допомогою додаткової системи фазового автопідстроювання частоти. В результаті дані, які в разі використання звичайної DDR SDRAM чекали б закінчення половини такту, доступні також через 1/4 і 3/4 такту. Теоретично в цьому випадку максимальна пропускна здатність повинна збільшитися вдвічі.

Стаття опублікована в журналі BYTE № 6 (47), червень 2002 р

Передруковується з дозволу автора.

Стаття надрукована в музей 17.02.2009